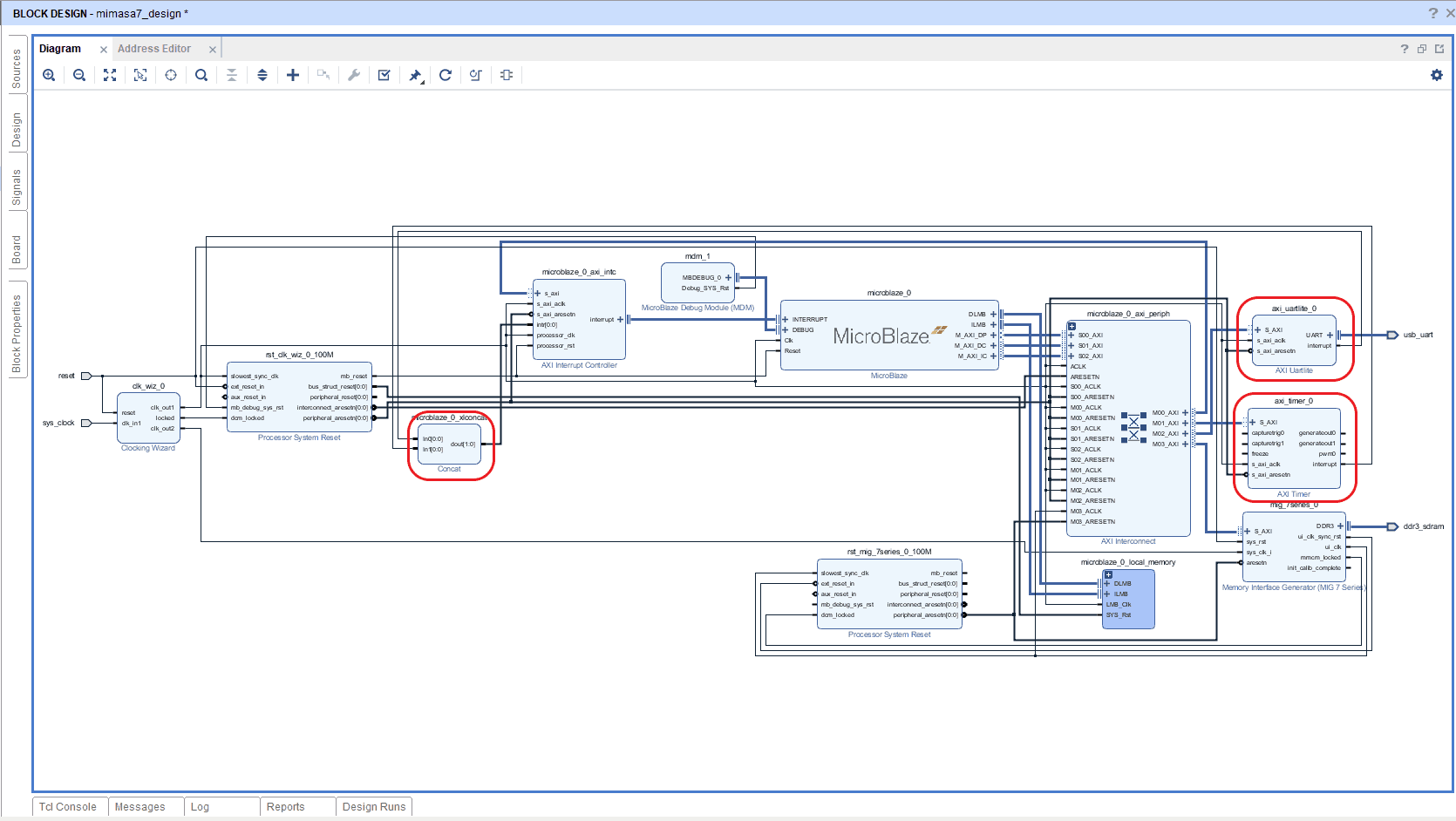

Vivado Design Suite – Create Microblaze based design using IP Integrator With Mimas A7 FPGA development board | Numato Lab Help Center

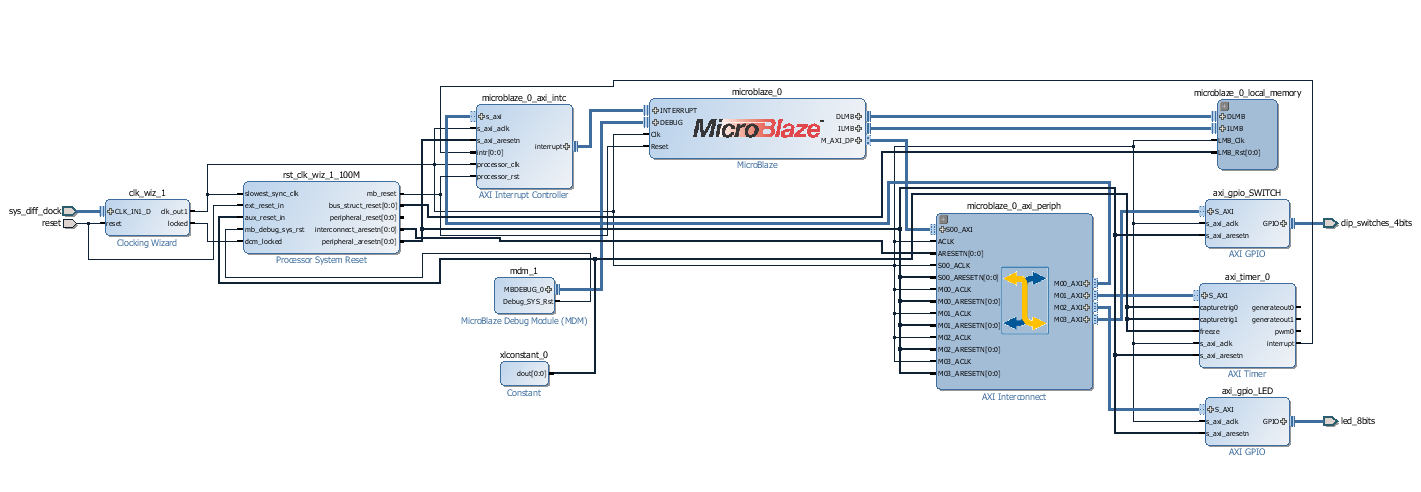

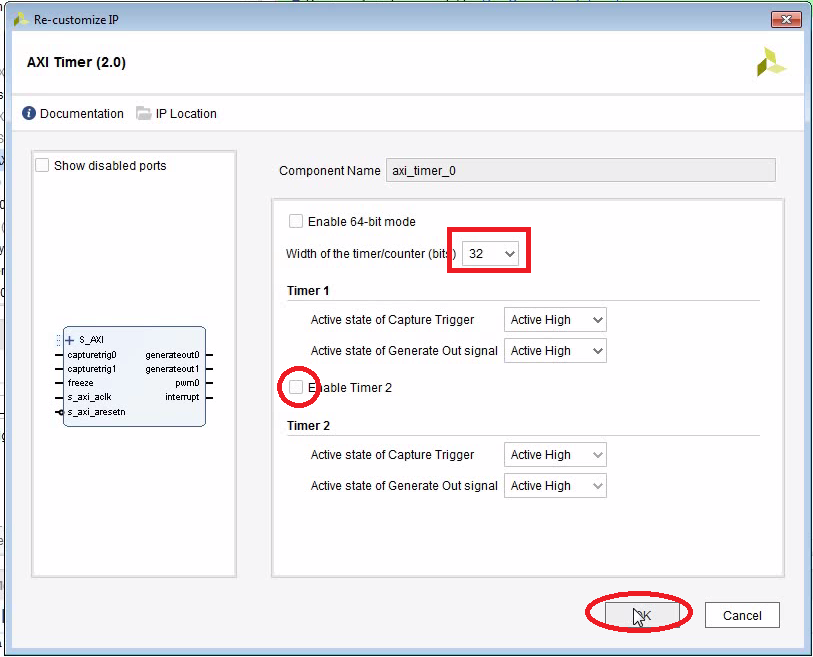

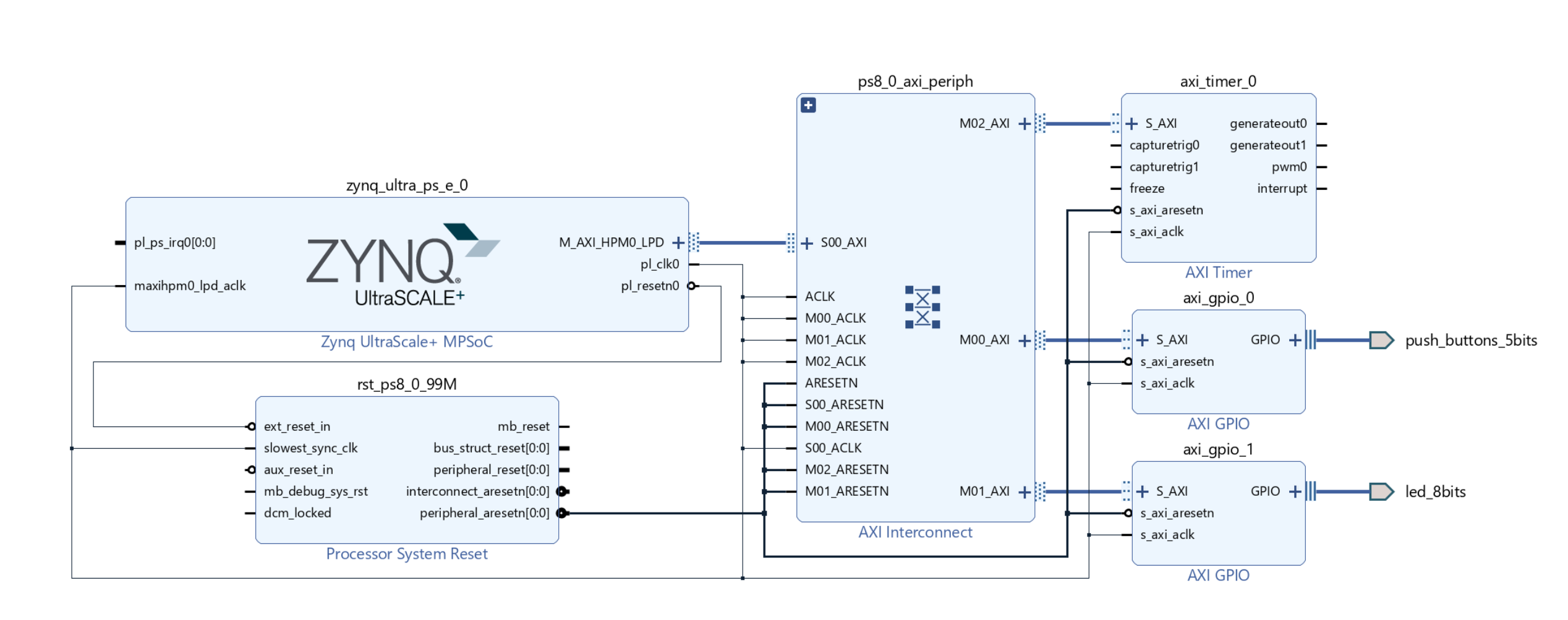

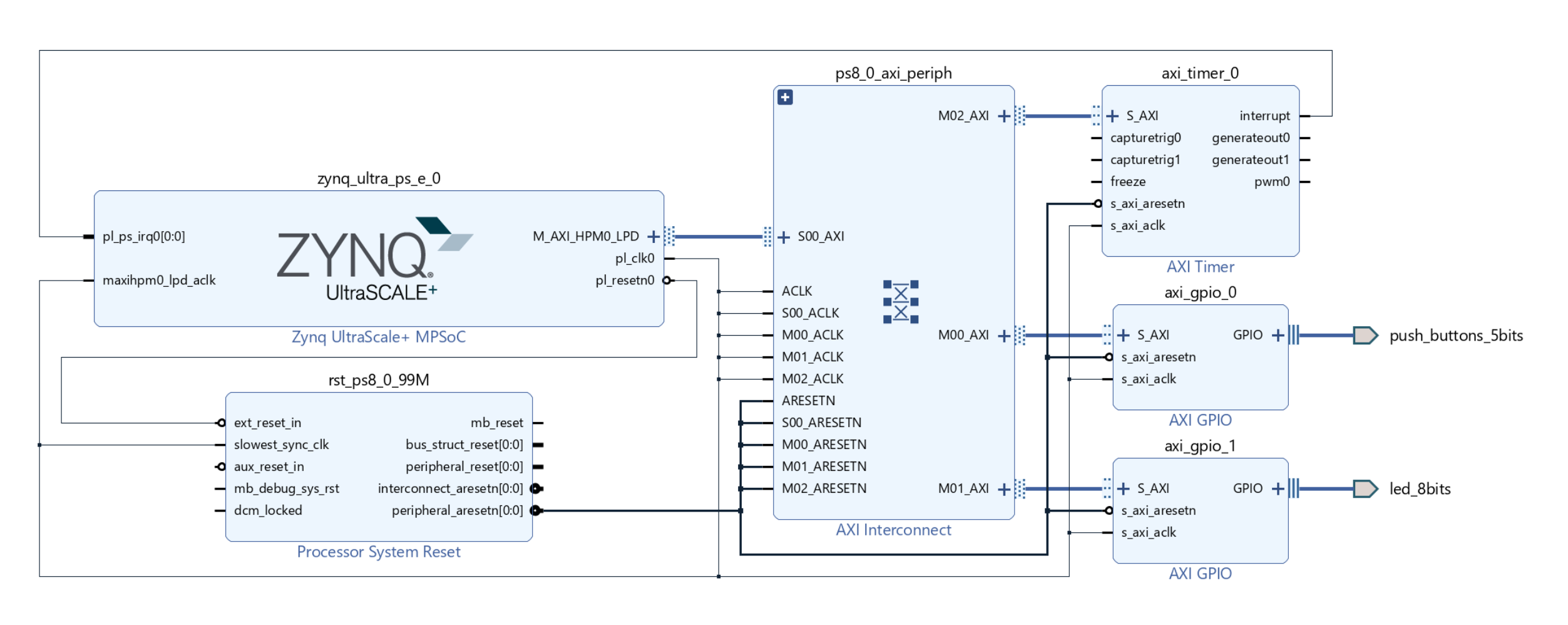

Design Example 1: Using GPIOs, Timers, and Interrupts — Embedded Design Tutorials 2021.1 documentation

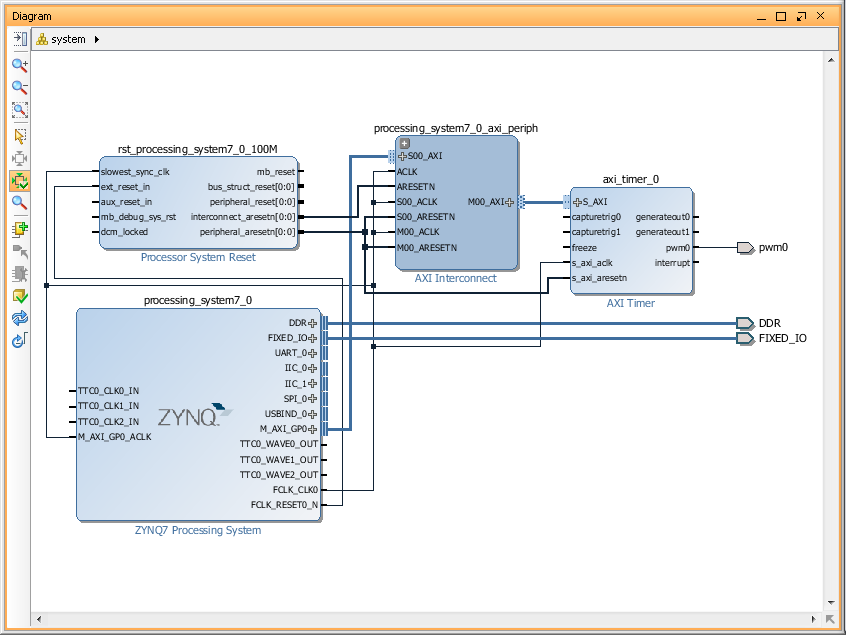

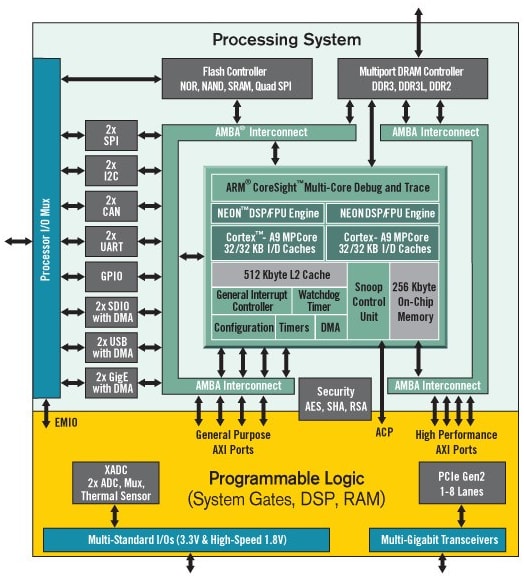

Design Example 1: Using GPIOs, Timers, and Interrupts — Embedded Design Tutorials 2021.1 documentation

IP Core Generation Workflow with a MicroBlaze processor: Xilinx Kintex-7 KC705 - MATLAB & Simulink - MathWorks Deutschland