VHDL synch reset for RTL logic in a Microblaze design - where to get it in my RTL synch counter logic?

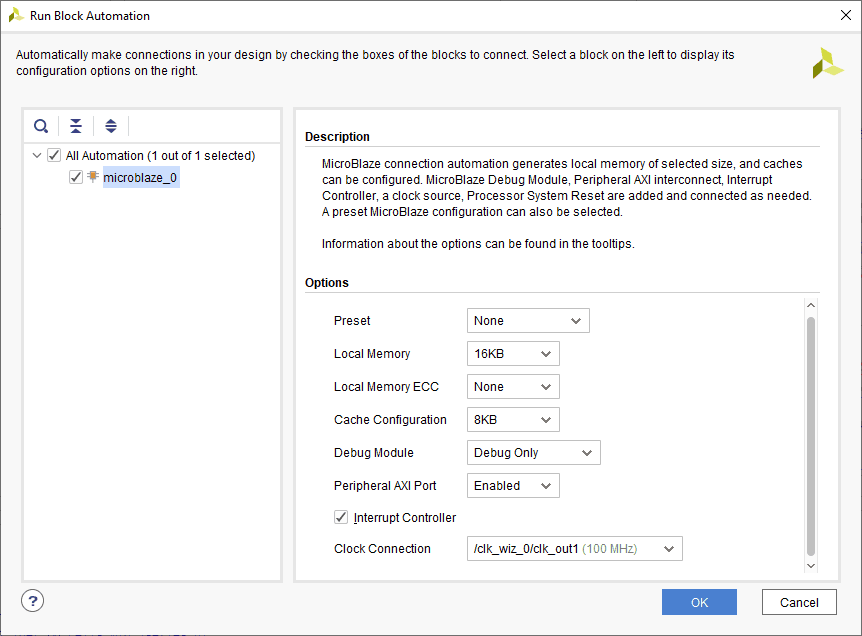

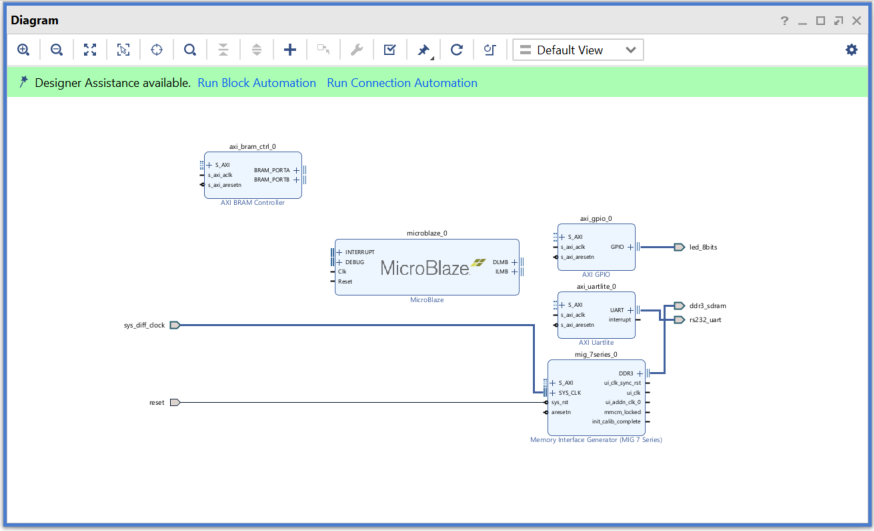

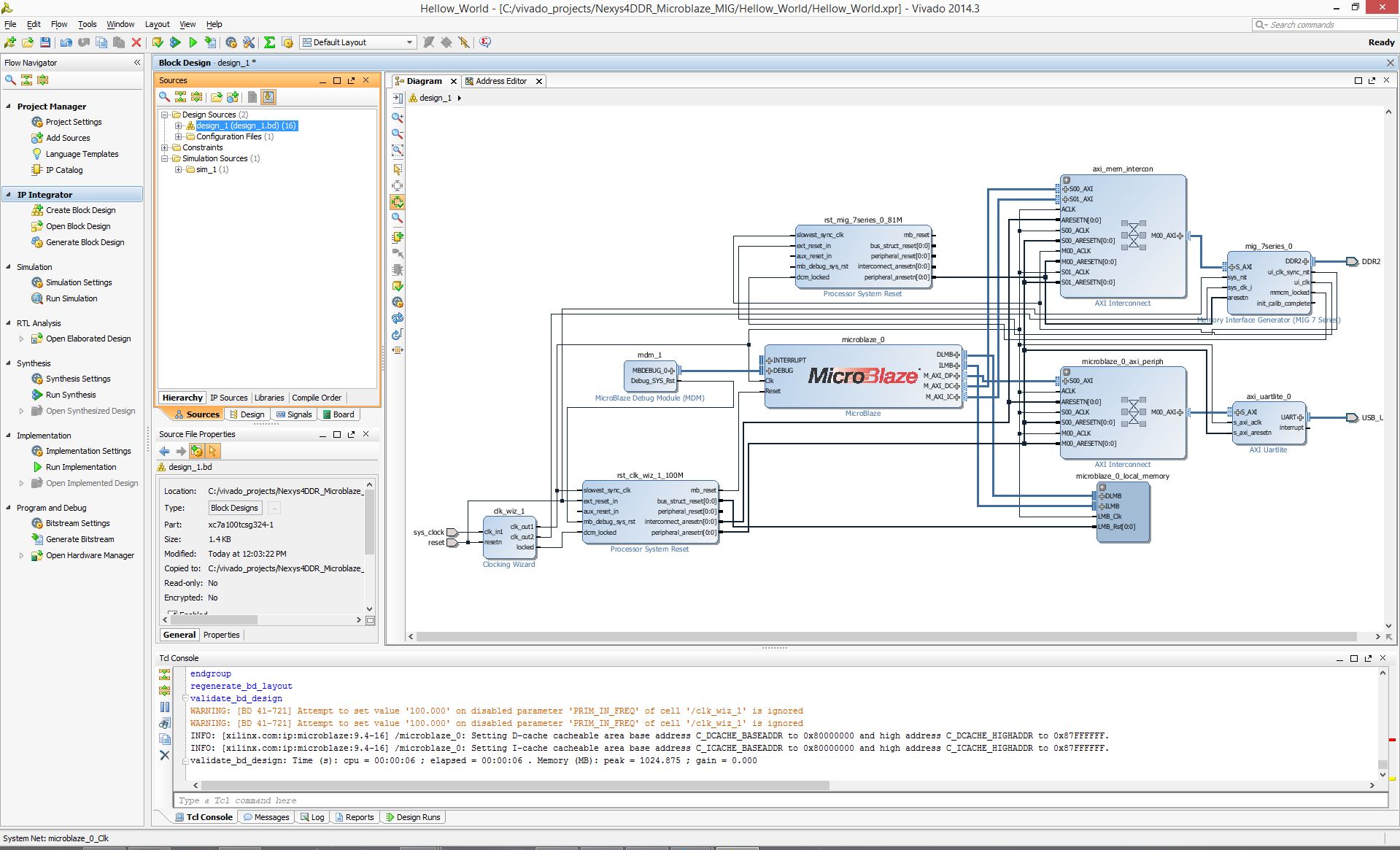

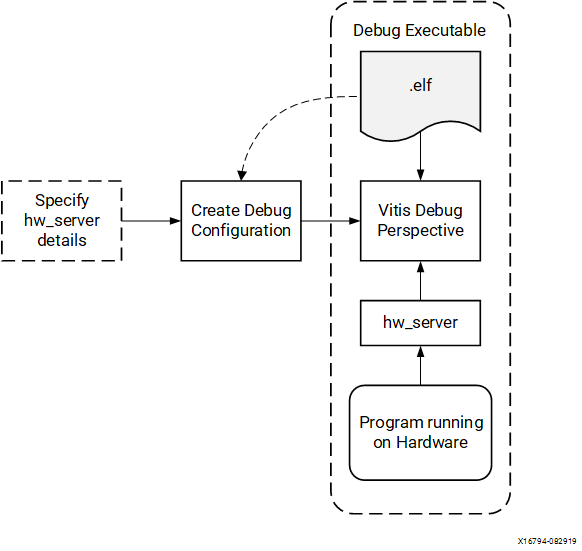

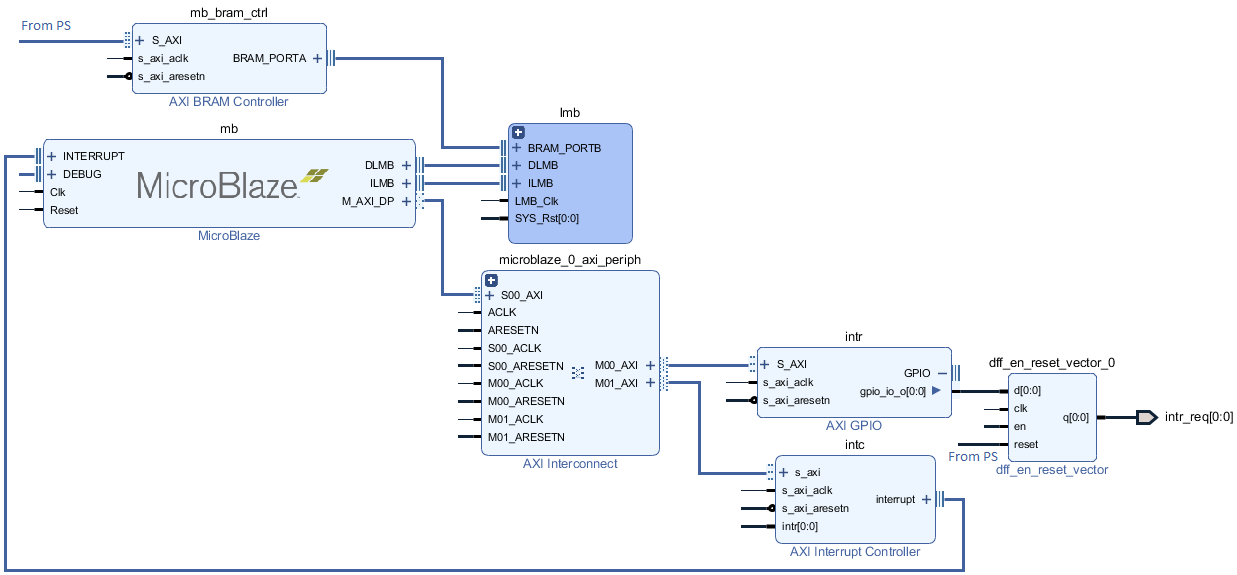

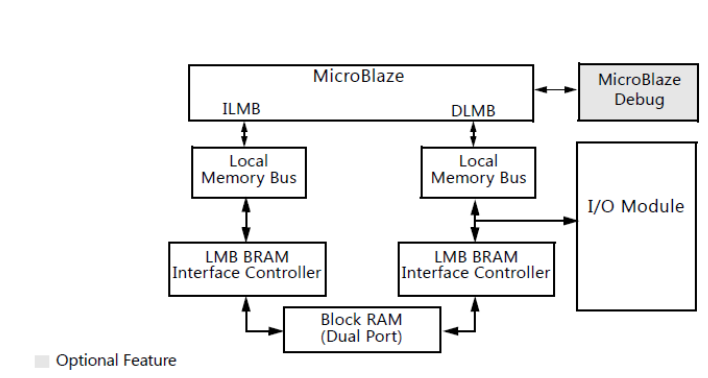

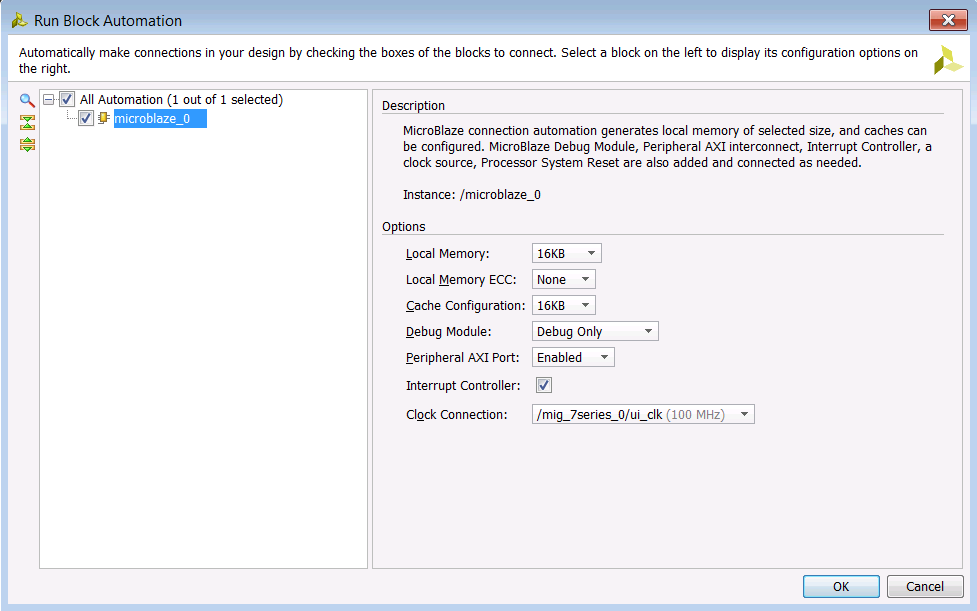

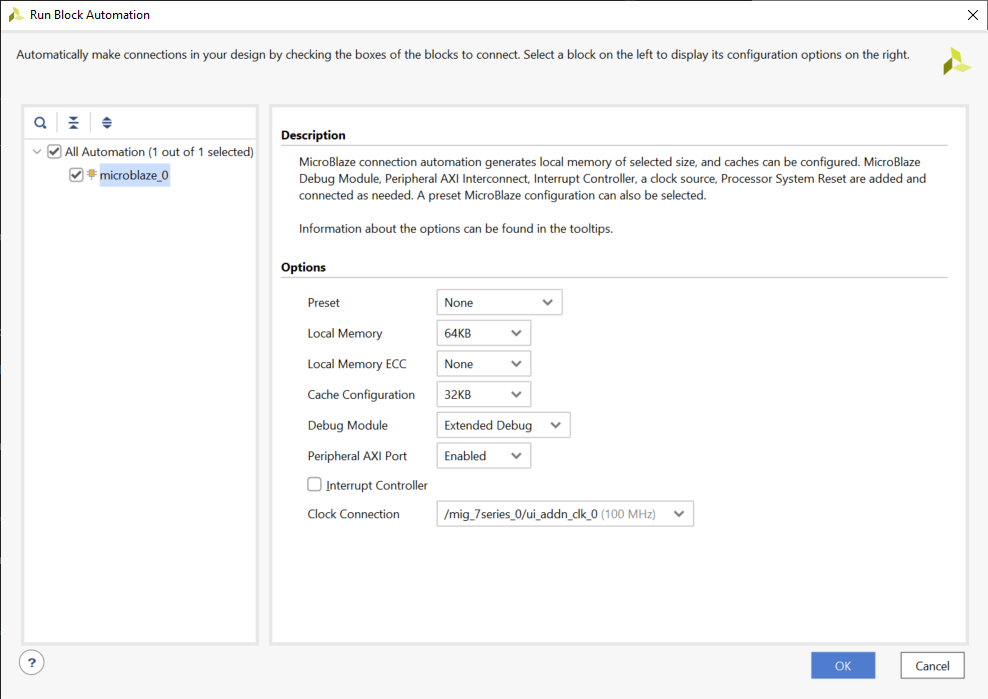

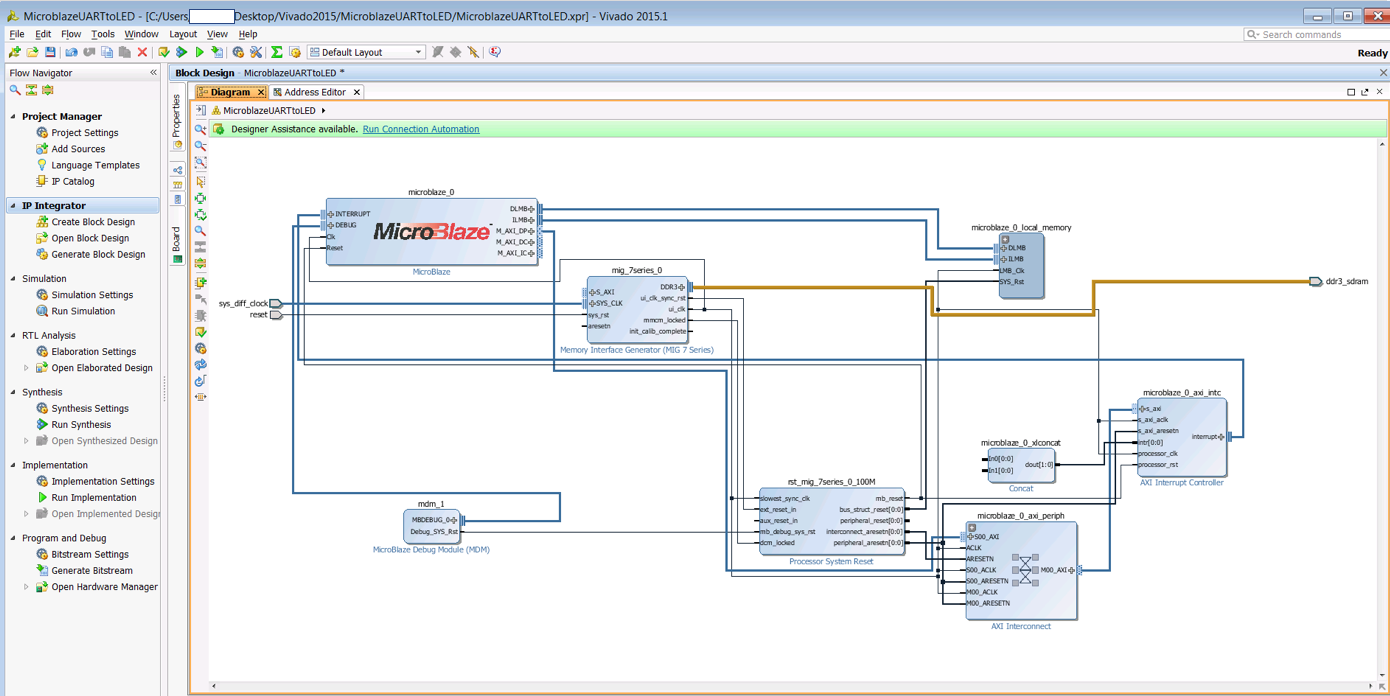

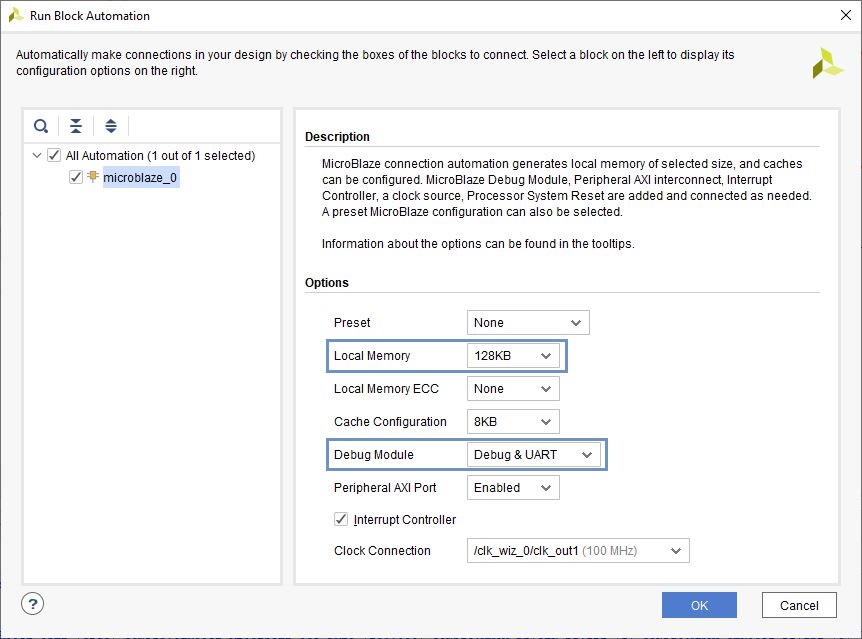

Vivado Design Suite – Create MicroBlaze based design using IP Integrator With Aller Artix-7 FPGA Board with M.2 Interface | Numato Lab Help Center