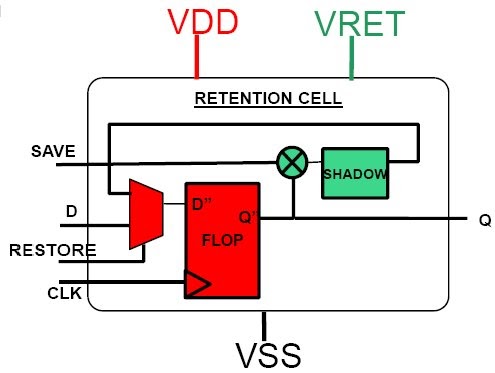

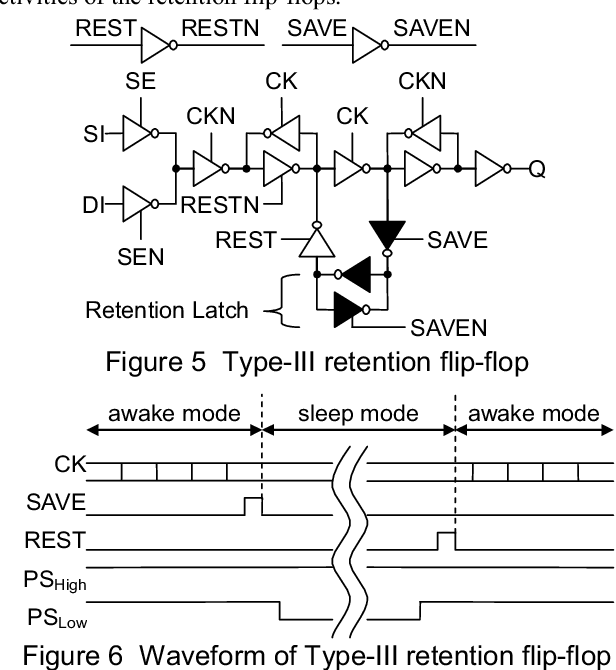

CIRCUIT ARRANGEMENT, A RETENTION FLIP-FLOP, AND METHODS FOR OPERATING A CIRCUIT ARRANGEMENT AND A RETENTION FLIP-FLOP - diagram, schematic, and image 08

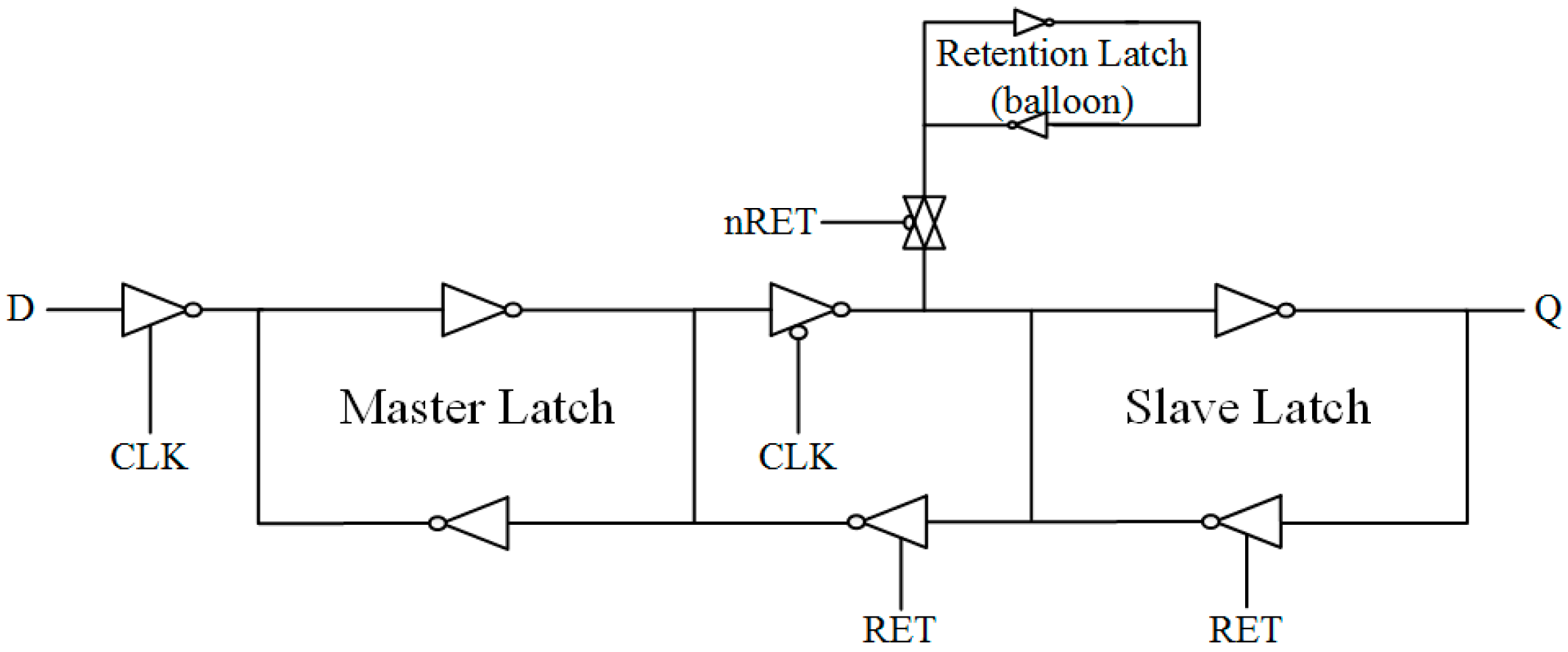

Figure 1 from A 0.4V 0.08fJ/cycle retentive True-Single-Phase-Clock 18T Flip -Flop in 28nm FDSOI CMOS | Semantic Scholar

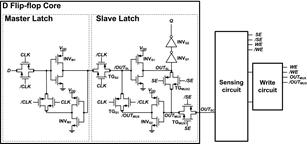

Timing diagram of Level Converting Retention Flip-Flop using LECTOR... | Download Scientific Diagram

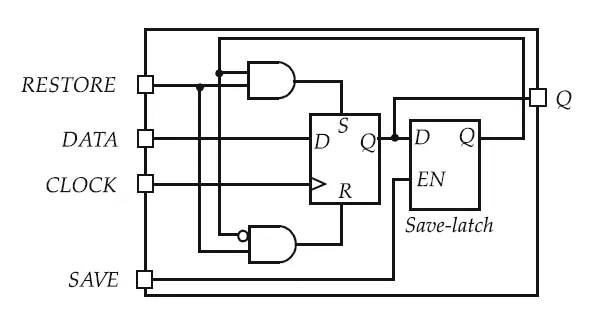

![PDF] Data-retention flip-flops for power-down applications | Semantic Scholar PDF] Data-retention flip-flops for power-down applications | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/3e2785c825677e2bae2eef279bce2fa7c1d0e573/2-Figure4-1.png)